Server-class RISC-V Core Unveiled by Ventana at RISC-V Summit

In a bid to bring RISC-V to the high-performance, data center computing space, Ventana announced their Veyron family, a series of processors positioned to offer the flexibility needed to drive innovation.

Choosing last week’s RISC-V summit as the venue, Ventana Micro Systems announced its upcoming Veyron V1 high performance RISC-V processor. The V1 is the first entrant to the Veyron family, a series of high performance chiplets and IP designed for server/data-center grade applications.

Ever since RISC-V was openly released in 2015,

it has gained considerable traction as an open, collaborative, and

extensible microprocessor. While other processor architectures are

proprietary, RISC-V ensures that anyone can use the architecture to

promote development and growth in the engineering and compute

communities.

An example Veyron V1 processor running at 3.6 GHz on a 5 nm process. Image used courtesy of Ventana Micro Systems

Building on this growth, Ventana’s Veyron family hopes to bring the RISC-V architecture to the data center, where companies can interface their own silicon to provide a customizable solution to extract maximum power and cost efficiency.

In this article, we’ll give an overview of Ventana’s RISC-V summit presentation alongside the key specs for the Veyron V1 processor. In addition, the broader implications of Ventana’s announcement are discussed to aid in understanding how the Veyron family can help designers in high-performance or server class settings.

Making Computing Open and Flexible

Led by founder and CEO Balaji Baktha, Ventana Micro Systems, a presentation at the RISC-V Summit has many engineers excited for the future of the architecture. At its core (processor pun not intended, but certainly appreciated), Ventana’s presentation highlighted the current state of the compute market.

The RISC-V architecture allows for designers and hyperscalers to extract maximum performance from their designs but it comes with hefty design costs. Competing architectures such as x86 or Arm offer a more turnkey solution, but don’t offer designer’s the flexibility that drives rapid innovation.

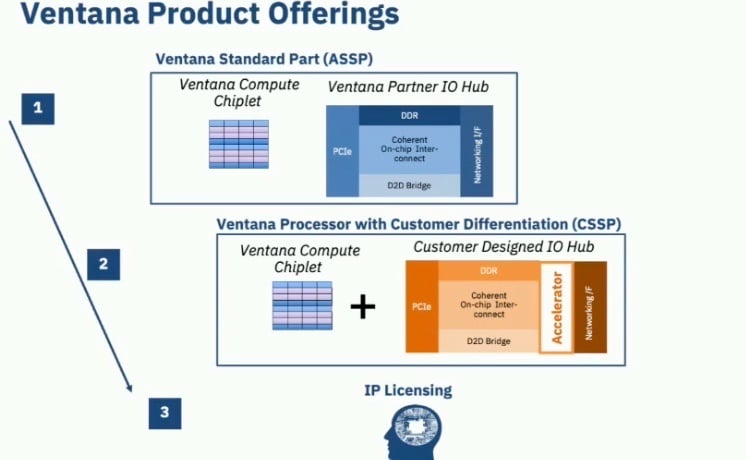

The Veyron processor offers designers the flexibility to include their own design differentiation when needed, in addition to an all-in-one solution.

Proposing a happy medium, Baktha gave viewers a preview of Ventana’s newest processor: the Veyron V1. Built on a 5 nm process, the V1 aims to give designers a modular solution that can be customized for a variety of use-cases.

For lighter applications, a single core can be used, whereas compute-heavy or data-heavy applications can optimize the number of cores or memory availability to optimize the performance without paying for unused resources.

In addition, instead of requiring designers to build their own innovations from the ground up, the Veyron V1 may offer engineers a “shortcut,” providing a working compute architecture on which they can add their own silicon. This solution not only helps keep BOM costs low, but allows designers to focus on their own contributions instead of spending resources on secondary design requirements.

Veyron: A High-Performance RISC-V Processor

Ventana’s Veyron V1, much like the French racer Pierre Veyron, hopes to demonstrate major speed and performance boosts compared to existing RISC-V processors. Under the hood, the V1 runs at 3.6 GHz with a total of 16 cores per cluster, scalability up to 128 cores, and 48 MB of shared L3 cache per cluster.

In addition, the V1 comes packed with features such as Advanced Interrupt Architecture, side channel attack security, and comprehensive RAS features, all of which are major benefits in server/data-center applications. Baktha claimed at the RISC-V summit that the single socket performance of the V1 is “second to none, none being anything in the world.”

The Ventana Veyron performance summary highlights the improvements offered by the family, including the low-latency die-to-die interconnects that make the chiplet modular. Ventana CEO Balaji Baktha (right). (Click image to enlarge)

Outside the technical specifications of the V1, Ventana has also released an SDK and development platform for use with the Veyron family, hoping to give designers a head start on the next generation of computing with the Veyron V1. The Veyron V1 is expected to be available in the second half of 2023, at which time the performance can be validated to get a comprehensive sense of the V1’s capabilities.

The Future of Open-Source Computing

Although it has served us faithfully for many years, it is no secret that Moore’s Law cannot hold indefinitely. As we approach maximum transistor density, it’s important to begin considering new ways to scale our computing performance. When discussing Ventana’s choice to target chiplets for the Veyron V1, Baktha referred to Bob Brennan in saying, “You can’t rely on transistors alone to drive performance and efficiency. That curve is flat. We need to come up with an alternative way to scale.”

A summary of target applications from Ventana highlights the flexibility introduced by the Veyron family, allowing designers to use the Veyron in all manner of applications.

By using chiplets instead of a single chip, designers can use the Veyron family to accomplish their desired task without overpaying for unneeded resources or compromising performance. The introduction of RISC-V processors to high-performance spaces gives engineers the ability to only select the features that are needed, and the inclusion of an SDK and a development kit helps to accelerate the inclusion of the Veyron family in the market.

Rivaling x86 and Arm Alternatives

Regardless of where the Veyron family eventually finds its niche, the announcement from Ventana is certainly exciting for the world of open-source computing. Baktha compared it to alternatives such as x86 and Arm processors.

“We can all be proud that we have a CPU that's performing at the same level as x86 or any of the Arm variants while providing something that's unique to RISC-V, which is open extensibility.”

As Ventana rolls out the Veyron family, it will be interesting to see how designers are able to incorporate the processor into their own solutions, and how RISC-V will help to drive the next generation of innovation.

All images from All About Circuits’ (virtual) attendance at the RISC-V Summit (except where otherwise specified)